# Двоичный АЦП прямого преобразования, 4-х битный

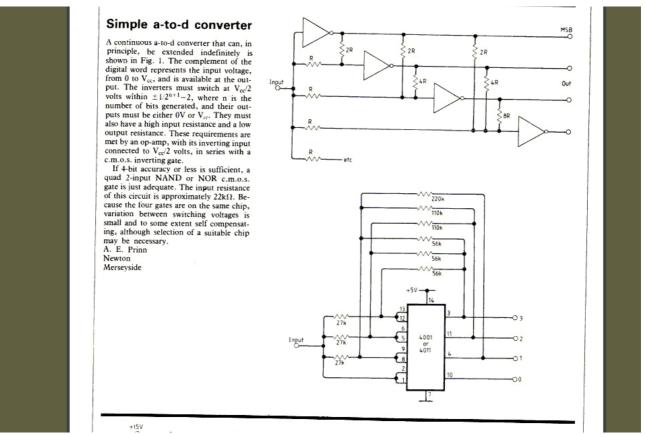

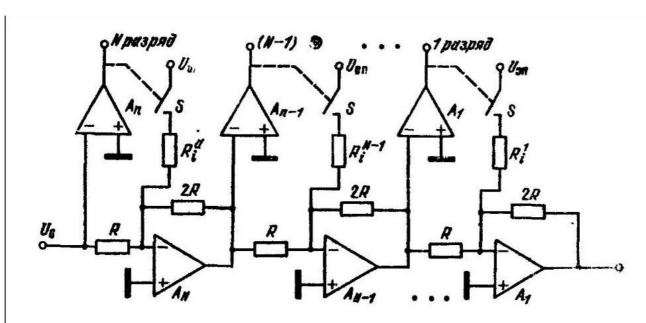

В литературе по электронике часто встречается схема униполярного 4-х битного двоичного АЦП прямого преобразования, разработанная Prinn'ом A. E. [1], приведённая на рис.1 и рис.2.

Рис. 1. Схема униполярного 4-х битного двоичного АЦП прямого преобразования из статьи Prinn'a «Simple a-to-d converter» в журнале «Wireless World» (Англия) Мау 1981, № 1544, р.60. [1]

В схеме применены только компараторы. Из-за отсутствия в схеме усилителей входной сигнал сильно затухает на каждой ступени АЦП.

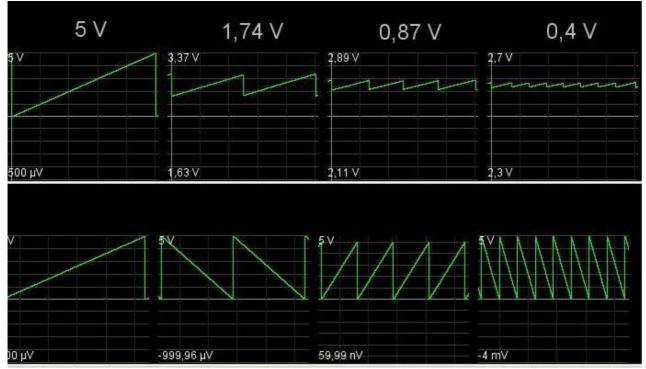

Недостатками схемы АЦП разработанной Prinn'ом являются:

- 1. Отсутствие усиления на всех ступенях АЦП, из-за чего входной сигнал с амплитудой 5 Вольт на входе второго компаратора имеет амплитуду 1,74 Вольта, на входе третьего компаратора 0,87 Вольта, а на входе четвёртого компаратора уменьшается более, чем в 10 раз, до 0,4 Вольта, что затрудняет увеличение количества ступеней (разрядов) АЦП.

- 2. Необходимость увеличения номиналов резисторов в 2 раза на каждой следующей ступени АЦП так же затрудняет увеличение количества ступеней (разрядов) АЦП.

- 3. Униполярность схемы АЦП удобна для применения в качестве компараторов логических элементов КМОП-логики (4001, 4011), но уменьшает область применения разработанного Prinn'ом АЦП.

## простой аналогоцифровой !

### **ПРЕОБРАЗОВАТЕЛЬ**

Простейший АДП может быть построен по схеме, приведенной на рис. 1. В ходное напряжение, которое может изменяться в днапазоне от нузя до напряжения источника питания (U<sub>n</sub>), представляется на выходах преобразователя в параллельном доподнительном двоичном коле

Аля нормальной работы АПП инверторы-компараторы  $\Lambda I = AI$  должны переключаться при цапряжении на их иходах, рав ном  $U_0/2$  с погрежностью не более  $U_n/(2^{n+1}/2)$  (и ислеразрядов выходное напряжения компараторов и устойчивых се-

стояниях должны быть ближими и нулю и  $U_{\rm p}$ . Кроме того, компараторы должны обладать высоким экодным и нирычм выходным сопротивлениями

Перечисленным требованизм удовлетворяют большинство современных ОУ, вивертирую щие входы которых подключены к потещиллу  $U_z/2$ .

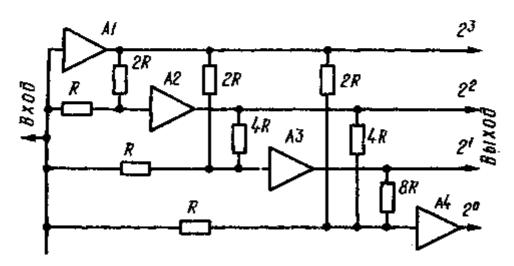

Если требуемви толность аналогоцифрового преобразования не превышает четыр у разрядов, то в качестве основы для АЦП можно использовать счетверенные КМОП логаческие элементы «И-НЕ» или «ИЛИ-НЕ». Один из вариантов такого устройства представлек на рис. 2. Его входьое сопротивление около 22 иОм, а время преобразования не более 300 нс.

"Wireless World" (Англия), май, 1981. № 1544

**Примечание редакции.** Отечественным аналогом микросхемы 4001 является К176ЛЕ5, а 4011 К176ЛА7.

Рис. 2. Схема униполярного 4-х битного двоичного АЦП прямого преобразования Prinn'а из статьи «Простой аналогоцифровой преобразователь» в советском журнале «РАДИО» № 8, 1982 г. стр.61 [2].

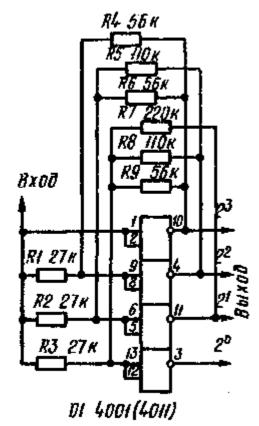

Рис. 2.22. Схемы АЦП на КМОП-инверторах:

Рис. 3. Схемы униполярного 4-х битного двоичного АЦП прямого преобразования Prinn'a из книжки Шило В. Л. Популярные цифровые микросхемы. М.: «Радио и связь», 1987. Стр. 219, Рис. 2.22. [3]

Рис. 4. Амплитуды пилообразного сигнала на входах четырёх компараторов АЦП Prinn'a (вверху) и АЦП, разработанного автором (внизу).

В обычной схеме преобразования, приведённой в [4] на Figure 2, входной сигнал

вычитателем на сумматоре сигналом, вырабатываемым компаратором и однобитным ЦАПом. В этой схеме входной сигнал не может быть больше половины максимального допустимого напряжения ОУ, иначе усиленный вдвое сигнал войдёт в режим ограничения. После умножения входного сигнала в 2 раза, усиленный вдвое сигнал сдвигается вычитателем на сумматоре на величину, вырабатываемую компаратором и однобитным ЦАПом. В результате, на выходе сумматора, амплитуда выходного сигнала не превышает половины наибольшей амплитуды входного сигнала и максимального допустимого напряжения ОУ. Из-за уменьшенного вдвое входного и выходного сигналов недоиспользуются усилительные свойства ОУ и в компараторах и в сумматорах.

Рис. 8.25. Преобразователь аналог — код со включением разрядов по цепочке

Рис. 5. Биполярный 4-х битный двоичный АЦП прямого преобразования с вычитанием и последующим умножением на 2 (усилением в 2 раза) [4].

Недостатком схемы на рис.5 является то, что для биполярного АЦП требуется переключение двух одинаковых по амплитуде, но разных по полярности опорных напряжений. В приведённой на рис.5 схеме подключается только одно опорное напряжение + Uon, второе же состояние, при разомкнутом ключе, является высокоимпедансным, с сопротивлением близким к бесконечности. Чтобы устранить этот недостаток требуется замыкающий ключ на два положения и одно направление 2П1Н заменить на переключающий ключ на два положения и два направления 2П2Н и подать второе опорное напряжение равное - Uon.

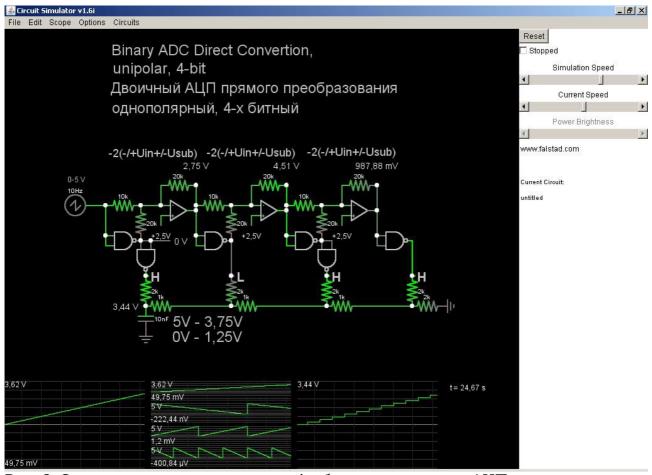

Рис. 6. Снимок модели униполярного 4-х битного двоичного АЦП прямого преобразования в симуляторе электронных схем Circuit Simulator v1.6i.

В разработанной автором схеме (Рис. 6) применён другой способ преобразования (Рис. 5) [5], в котором инвертирующий объединённый «сумматор-умножитель на 2» делит входную проходную характеристику на две части в середине определяемой объединённым «компаратором-однобитным ЦАПом», затем и первая и вторая половины проходной характеристики сдвигаются объединённым «компаратором-однобитным ЦАПом» и инвертирующим объединённым «сумматором-умножителем на 2» на разные величины таким образом, чтобы середины вновь образованных двух проходных характеристик оказались бы в середине амплитуд входных сигналов. Затем разность усиливается в 2 раза инвертирующим объединённым «сумматором-умножителем на 2».

В модели униполярного 4-х битного двоичного АЦП прямого преобразования, приведённой на рис. 6, ослабление сигнала в 2 раза на каждой ступени компенсируется усилением сигнала в 2 раза на каждой ступени, что позволят увеличивать количество ступеней (разрядов) АЦП.

Все ступени АЦП — одинаковые, с одинаковыми, не возрастающими, номиналами резисторов, что облегчает увеличение количества ступеней (разрядов) АЦП.

Модель разработана для показания возможности и способа построения двоичных АЦП прямого преобразования.

Количество уровней дискретизации равно 2^n, где n - число разрядов (ступеней).

Аппаратные затраты в двоичных АЦП равны 2\*n-1 ОУ.

Время преобразования равно (2n-1)\*dtoy, где dtoy — время задержки в одном ОУ (в объединёном «компараторе-однобитном ЦАПе» на ОУ и в инвертирующем объединённом «вычитателе-умножителе на 2» на ОУ).

### Литература:

- 1. WIRELESS WORLD MAY 1981, p.60. "Simple a-to-d converter", A. E. Prinn.

- 2. «Простой аналогоцифровой преобразователь», «РАДИО» № 8, 1982 г., стр.61.

- 3. Шило В. Л. Популярные цифровые микросхемы. М.: «Радио и связь», 1987. Ctp. 219, Рис. 2.22. <a href="http://nashol.com/2011041454419/spravochnik-populyarnie-cifrovie-mikroshemi-shilo-v-l.html">http://nashol.com/2011041454419/spravochnik-populyarnie-cifrovie-mikroshemi-shilo-v-l.html</a>

- 4. ANALOG DEVICES MT-025 TUTURIAL. ADC Architectures VI: Folding ADCs by Walt Kester.

- 5. Шило В. Л. Линейные интегральные схемы в радиоэлектронной аппаратуре. М.: «Советское радио», 1979. Стр. 341, Рис. 8.25. Преобразователь аналог код со включением разрядов по цепочке. http://publ.lib.ru/ARCHIVES/SH/SHILO Valeriy Leonidovich/ Shilo V.L..html

- 6. Онлайн-версия симулятора электронных схем "Circuit Simulator", Поля Фальстада (США).

Куликов А.С., Россия-Русь, Москва, Царицыно, версия от 16.06.2019 г.

#### Приложение 1.

Код модели униполярного 4-х битного двоичного АЦП прямого преобразования в симуляторе электронных схем Circuit Simulator v1.6i (можно импортировать в онлайн-версию симулятора электронных схем Circuit Simulator version 2.1.14 јѕ Поля Фальстада):

#### Файл:

http://andserkul.narod.ru/ADC DirectConvertion All-Serial Unipolar 4-bit 5V.noext